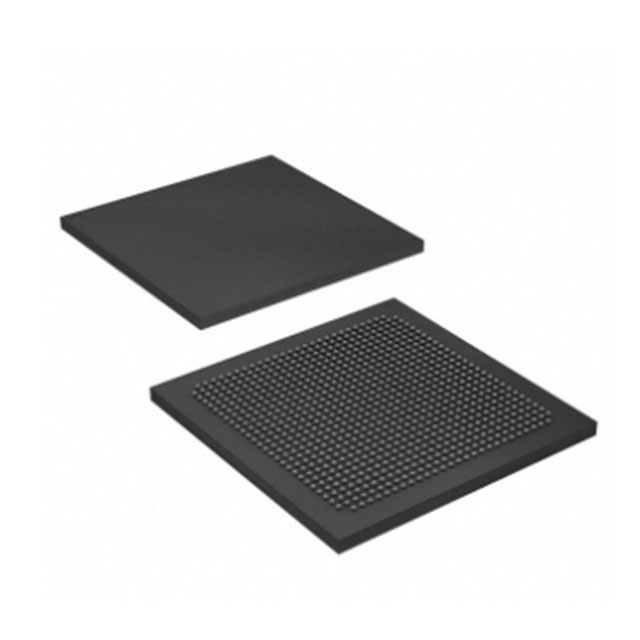

5CEFA5F23I7N Cyclone® VE Field Programmable Gate Array (FPGA) IC 240 5001216 77000 484-BGA

គុណលក្ខណៈផលិតផល

| ប្រភេទ | គូររូប |

| ប្រភេទ | អារេច្រកទ្វារដែលអាចសរសេរកម្មវិធីបាន (FPGAs) |

| ក្រុមហ៊ុនផលិត | ក្រុមហ៊ុន Intel |

| ស៊េរី | ព្យុះស៊ីក្លូន® VE |

| រុំ | ថាស |

| ស្ថានភាពផលិតផល | សកម្ម |

| DigiKey គឺអាចសរសេរកម្មវិធីបាន។ | មិនបានផ្ទៀងផ្ទាត់ |

| លេខ LAB/CLB | ២៩០៨០ |

| ចំនួនធាតុ/ឯកតាតក្កវិជ្ជា | ៧៧០០០ |

| ចំនួនសរុបនៃ RAM ប៊ីត | ៥០០១២១៦ |

| I/O 數 | ២៤០ |

| វ៉ុល - ការផ្គត់ផ្គង់ថាមពល | 1.07V ~ 1.13V |

| ប្រភេទនៃការដំឡើង | ប្រភេទ adhesive ផ្ទៃ |

| សីតុណ្ហភាពប្រតិបត្តិការ | -40°C ~ 100°C (TJ) |

| កញ្ចប់/លំនៅដ្ឋាន | ៤៨៤-BGA |

| ការវេចខ្ចប់សមាសធាតុអ្នកលក់ | 484-FBGA (23x23) |

| លេខមេផលិតផល | 5CEFA5 |

ការណែនាំអំពីផលិតផល

ឧបករណ៍ Cyclone® V ត្រូវបានរចនាឡើងក្នុងពេលដំណាលគ្នា ដើម្បីសម្រួលដល់ការប្រើប្រាស់ថាមពល ការចំណាយ និងពេលវេលាពីទីផ្សារធ្លាក់ចុះ។និងការកើនឡើងតម្រូវការកម្រិតបញ្ជូនសម្រាប់កម្មវិធីដែលមានបរិមាណខ្ពស់ និងតម្លៃដែលរសើប។ធ្វើឱ្យប្រសើរឡើងជាមួយនឹងឧបករណ៍បញ្ជូនទិន្នន័យរួមបញ្ចូលគ្នា និងឧបករណ៍បញ្ជាអង្គចងចាំរឹង ឧបករណ៍ Cyclone V គឺសមរម្យសម្រាប់កម្មវិធីនៅក្នុងទីផ្សារឧស្សាហកម្ម បណ្តាញឥតខ្សែ និងខ្សែ យោធា និងរថយន្ត។

លក្ខណៈពិសេសផលិតផល

បច្ចេកវិទ្យា

- បច្ចេកវិទ្យាដំណើរការថាមពលទាប 28-nm (28LP) របស់ក្រុមហ៊ុន TSMC

- វ៉ុលស្នូល 1.1 V

ការវេចខ្ចប់

- Wirebond កញ្ចប់ halogen ទាប

- ដង់ស៊ីតេឧបករណ៍ច្រើនជាមួយនឹងបាតកញ្ចប់ដែលត្រូវគ្នាសម្រាប់ការធ្វើចំណាកស្រុកដោយគ្មានថ្នេររវាងដង់ស៊ីតេឧបករណ៍ផ្សេងៗគ្នា

- អនុលោមតាម RoHS និងជម្រើសនាំមុខ

ក្រណាត់ FPGA ដែលមានប្រសិទ្ធភាពខ្ពស់។

- ធ្វើឱ្យប្រសើរឡើង 8-បញ្ចូល ALM ជាមួយការចុះឈ្មោះចំនួនបួន

ប្លុកអង្គចងចាំខាងក្នុង

- ប្លុកអង្គចងចាំ M10K—10 គីឡូបៃ (Kb) ជាមួយនឹងកូដកែកំហុសទន់ (ECC)

- ប្លុកអារេតក្កវិជ្ជាអង្គចងចាំ (MLAB)—640-ប៊ីត LUTRAM ចែកចាយដែលអ្នកអាចប្រើរហូតដល់ 25% នៃ ALMs ជាអង្គចងចាំ MLAB

ប្លុក IP រឹងដែលបានបង្កប់

- ការគាំទ្រដើមសម្រាប់កម្រិតភាពជាក់លាក់នៃការដំណើរការសញ្ញារហូតដល់បី (បី 9 x 9 ពីរ 18 x 18 ឬមួយ 27 x 27 មេគុណ) នៅក្នុងប្លុក DSP ភាពជាក់លាក់អថេរដូចគ្នា

- 64-bit accumulator និង cascade

- អង្គចងចាំមេគុណខាងក្នុងដែលបានបង្កប់

- Prereadder/subtractor សម្រាប់បង្កើនប្រសិទ្ធភាព

- DDR3, DDR2 និង LPDDR2 ជាមួយនឹងការគាំទ្រ ECC 16 និង 32 ប៊ីត

- PCI Express* (PCIe*) Gen2 និង Gen1 (x1, x2, ឬ x4) hard IP ជាមួយនឹងការគាំទ្រពហុមុខងារ ចំណុចបញ្ចប់ និងច្រកឫស

ការកំណត់រចនាសម្ព័ន្ធ

- ការការពារ amper - ការការពារការរចនាដ៏ទូលំទូលាយដើម្បីការពារការវិនិយោគ IP ដ៏មានតម្លៃរបស់អ្នក។

- លក្ខណៈសុវត្ថិភាពនៃការរចនាស្តង់ដារអ៊ិនគ្រីបកម្រិតខ្ពស់ (AES) ប្រសើរឡើង

- CVP

- ការកំណត់រចនាសម្ព័ន្ធថាមវន្តនៃ FPGA

- សៀរៀលសកម្ម (AS) x1 និង x4 សៀរៀលអកម្ម (PS) JTAG និងជម្រើសកំណត់រចនាសម្ព័ន្ធប៉ារ៉ាឡែលអកម្មលឿន (FPP) x8 និង x16

- ជូតខាងក្នុង (2)

- ការកំណត់រចនាសម្ព័ន្ធឡើងវិញដោយផ្នែក (3)

សរសេរសាររបស់អ្នកនៅទីនេះ ហើយផ្ញើវាមកយើង